# **4TH GENERATION VOTING MACHINE**

Dr. M G Gireeshan1, Akhilesh K2

Research Scientist Biomedical department1, Bharath University, Chennai India

EEE department2, Nehru College of engineering and research Centre, Trissur, Kerala, India

**ABSTRACT:** 4TH GENERATION VOTING MACHINE is that it is compactable and user friendly. It will be more secure if this system is implemented along with the ATM facility. This technology hasn't been launched yet .We anticipates it will come true in future .We hope it will be a better alternative for our sophisticated life style. The project is the very important and useful

Keywords: Microcontroller, Microprocessor, Touch pad, Transmitter, Oscillator.

# 1. INTRODUCTION

The machines have two parts

#### 1. Touch pad

#### 2. Memory unit.

The memory unit in which where the vote is recorded .The polling officer can control the Touch pad even from a very distant place of more than one KM. The machine can also control be a digital camera. The touch can be placed in the polling booth through which the voters can vote as usual by the permission of the polling officer who is in a distant place keeping the memory unit through a closed circuit T.V. The authority in the polling booth can verify the voters list, Register, Identity card and all. The same method of inking can also be done as usual. It prevents all types of malpractices, booth attack and booth capture. The capacity of the system is very high whereas the cost of the product is very low. Speedy safety and accuracy. This technology is very important and useful. A photograph of the machine is also attached for favorable consideration. It will be more secure if this system is implemented along with the ATM facility. This technology hasn't been launched yet.

## 1.1 Touch pad

## 2. ADVANTAGES OF EMBEDDED SYSTEM

- HIGHER PERFOMANCE: The integration of various ICs shortens the traveling route and time of a data to be transmitted resulting in higher performance

- LOWER POWER CONSUMPTION: The integration of various ICs eliminates buffers and other interface circuits. As the number of components is reduced less power will be consumed

- SLIMMER AND MORE COMPACT: Housed in a single separate package, the chip is smaller in size and therefore occupies less space on the PCBs. Hence product using embedded system is slimmer and more compact.

- REDUCED DESIGN AND DEVELOPMENT SYSTEM: The system on a chip provide all the functionally required by the system. System designers need not worry about basic function of the system-right from the beginning of the design phase, they can focus on the development on new features. As a result the time spends on research and development is reduced and this turn reduces the time to market their products.

- LOWER SYSTEM COSTS: In the past, several chips in separate packages were required to configure a system. Now just one system – on chip can replace all of these, dramatically reducing the packaging cost.

The microcontroller PIC16F73 is manufactured by MICROCHIP. This IC was selected because of its lower cost and availability of different series and type suitable for our requirements. It comes under RISC (Reduced Instruction Set Computer). It has only 35 instructions and so it is very easy to program.

The microcontroller is selected because of its advantage over the microprocessors. Microprocessor is a system on board. It needs a number of peripheral devices to work as a system. In microcontroller ADC, Timers, Counters, I/O Ports, USART etc are on a single chip. This helps to reduce the size of our equipment.

The microcontroller PIC16F73 has Flash memory. So if there is any correction in the program it could be erased and a new program can be added.

PIC micro devices are grouped by the size of their instruction word.

The three current PIC micro families are:

Base-Line : 12-bit instruction word length Mid-Range: 14-bit instruction word length High-end : 16-bit instruction word length

# **3. DEVICE STRUCTURE**

Each part of a device can placed into one of three groups: 1. Core

- 2. Peripherals

- 3. Special Features

# **3.1 THE CORE**

The core pertains to the basic features that are required to make the device operate.

These includes

- Device oscillator

- Reset logic

- CPU(Central Processing Unit)

- ALU(Arithmetic Logic Unit)

- Device memory map organization

- Interrupt Operation

- Instruction set revision

## 3.2 PERIPHERALS

Peripherals are the features that add a differentiation from a microprocessor. These ease in interfacing to the external world (such us general purpose I/O, LCD drives A/D inputs and PWM outputs), and internal tasks such as keeping different time bases (such us timers).The peripherals are: 1 TIMER 0

| 1. | TIMER |  |

|----|-------|--|

|    |       |  |

2. TIMER 1

3. TIMER 2

| 1. ADC       |  |

|--------------|--|

| 5. I/O PORTS |  |

| 5. USART     |  |

| 7. CCP       |  |

## **3.3 SPECIAL FEATURES**

Special features are the unique features that help to decrease system cost or increase system reliability or increase system flexibility. The PIC microcontroller offers several features that help to achieve these goals. The special features discussed are:

- 1. Device configuration bits

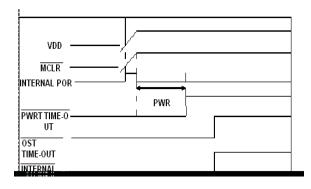

- 2. On-chip Power-On Reset (POR)

- 3. Brown-Out Reset (BOR) LOGIC

- 4. Watchdog timer

- 5. Low power mode (sleep mode)

#### 4. OSCILLATOR

The internal oscillator circuit is used to generate the device clock. The device clock is required for the device to execute instructions and for the peripherals to function. Four device clock periods generate one internal clock cycle. There are up to eight different modes which the oscillator may have. There are two modes which allows the selection of the internal RC oscillator clock out (CLK OUT) to be driven on an I/O pin, or allow that I/O pin to be used for a general purpose function. The oscillator mode is selected by the device configuration bits. The device configuration it's are nonvolatile memory locations and the operating mode is determined by the value written during device programming. The oscillator modes are:

- LP Low frequency (power) Crystal

- XT Crystal / Resonator

- HS High Speed Crystal / Resonator

- RC External Resistor / Capacitor (same as EXTRC with CLKOUT)

- EXTRC External Resistor / Capacitor

- EXTRC External Resistor / Capacitor with CLKOUT

- INTRC Internal 4MHz Resistor / Capacitor

- INTRC Internal 4MHz Resistor / Capacitor with CLKOUT

#### 4.1 Data Memory Organization

Data memory is made up of the special function registers area, and the general purpose registers area. The SFR controls the operation of the device while GPR are the general area for data storage and scratch pad operations. The data memory is banked for both the GPR and SFR area. The GPR area banked to allow greater than 96 bytes of general purpose RAM to be addressed. SFR are for the registers are that control the peripherals and core functions. Banking requires the use of controlled the bank selection. The control bits are located in STATUS register (STATUS <7:5). To move values from one register to another register, the value must pass through the working register (w). This means than for all register to register moves; two instruction cycles are required . The entire data memory can be accessed either directly or indirectly. Direct addressing may require the use of the RP1: RP0 bits. Indirect addressing requires the use of file select register. Indirect addressing uses the Indirect Register Pointer (IRP) bit of the STATUS register for accesses In the Bank 0 / Bank 1 or the Bank 2 / Bank 3 areas of the data memory.

#### 4.2 Banking

The data memory is partitioned in to four Banks. Each Bank Contains GPRs and SFRs. Switching between these Banks requires the RP0 and RP1 bits in the STATUS register to be configured for each bank extends up to 7Fh(128 bytes). The lower locations of each bank are reserved for the SFRs. above the Special Function Registers are the General Purpose registers. All data memory is implemented as static RAM. Some "high use "SFRs from the Bank0 are mirrored in the other banks for the core reduction and quicker access.

#### 4.3 Ports

General-purpose I/O pins can be considered as the simplest of peripherals. They allow the PIC micro controller to monitor and control other devices. To add flexibility and functionality to a device, some pins are multiplexed with an alternate function(s). These functions depend on which peripherals features are on the device. In general, when peripheral is functioning, that pin may not be used as a general purpose I/O pin. For most ports, the I/O pin's direction (input or output) is controlled by the data direction register, called the TRIS register. TRIS<x> controls the direction of PORT<x>. A '1' in the TRIS bit corresponds to that pin being an input, while a '0' corresponds to that pin being an output. An easy way to remember is that a '1' looks like an I (input) and '0' looks like an O (output). The PORT register is the latch for the data to be output. When the PORT is read, the device reads the levels presents on the I/O pins.

#### 4.4 PORT A and the TRISA REGISTER

The RA4 pins is a Schmitt Trigger input and a open drain output. All other RA port pins have TTL input levels and full CMOS Output drivers. All pins have a data direction bits (TRIS registers), which can configure these pins as output or input. Setting a TRISA register bit puts the corresponding output driver in a high impedance International Journal of Scientific & Engineering Research, Volume 5, Issue 7, July-2014 ISSN 2229-5518

mode. Clearing a bit in the TRISA register puts the contents of the output latch on the selected pin(s).

## 4.5 PORT B and the TRISB REGISTER

PORTB is an 8- bit wide bi-directional port. The Corresponding data direction register is TRISB. Setting a bit in the TRISB register puts the corresponding output driver in hi-impedance Input mode. Clearing a bit in the TRISB register puts the contents of the output latch on the selected pin(s).

#### 4.6 PORT C and the TRISC REGISTER

PORT C is an 8-bit bi- directional port. Each pin is individually configurable as an input or output through the TRISE register. PORTC pins have Schmitt Trigger input buffers. When enabling peripherals functions, care should be taken in defining TRIS bits for each PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other peripherals override the TRIS bit to make a pin an input.

#### **PROGRAMMABLE INTERFACE CONTROLLER (PIC)** WHY PIC IS USED?

**SPEED**: When operated at its maximum clock rate, a PIC executes most of its instructions in 0.2 microsecond or 5 instructions /microsecond.

- HIGH PERFORMANCE RISC CPU

- INSTRUCTION SET SIMPLICITY:

The instruction set consists of 35 instructions.

• INTEGRATION OF OPERATIONAL FEATURES:

Power –on reset and brown out protection ensure that the chip operates only when the supply voltage is within specification; a watchdog timer resets the PIC if the chip ever malfunctions and deviates its normal operations. Any one of four clock options can be supported, including a low cost RC oscillator and a high accuracy crystal oscillator.

• PROGRAMMABLE TIMER OPTIONS:

Three versatile timers can be characterize inputs, control outputs and provide internal timing for program executions.

• INTERRUPT CONTROL:

Up to 12 independent interrupt sources, which can provide useful interrupting as and when needed.

- EPROM/OTP/ROM OPTIONS:

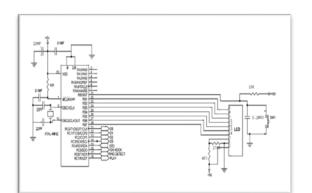

- Fig.3 Connection of PIC microcontroller with LCD Display

Ultraviolet erasable, programmable parts support Development. Lower cost one time programmable parts support both small and large productions runs.

• IN-BUILT MODULES:

The PIC micro controller has a number of inbuilt modules like ADC, USART that increase versatility of micro controller.

- LOW POWER CONSUMPTION

- WIDE OPERATING VOLTAGE RANGE: 2.5 TO

6.0 V

- PROGRAMMABLE CODE PROTECTION MODE

- POWER SAVING SLEEP MODE

#### **5. CIRCUIT DESCRIPTION**

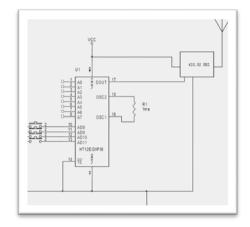

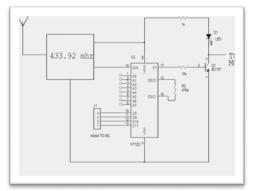

The above circuit diagram shows the working of 4<sup>th</sup> Generation Voting Machine. It includes the following section:

1. TRANSMITTER

- 2. RECEIVER

- 3. PIC MICROCONTROLLER

- 4. LIQUID CRYSTAL DISPLAY

IJSER © 2014 http://www.ijser.org

#### International Journal of Scientific & Engineering Research, Volume 5, Issue 7, July-2014 ISSN 2229-5518

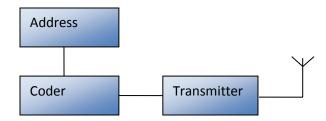

Fig1 Connection of Data Encoder and Transmitter

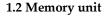

Fig2 Connection of PIC microcontroller with Data receiver

# 6. CONCLUSION

It will be more secure if this system is implemented along with the ATM facility. This technology hasn't been launched yet .We anticipates it will come true in future .We hope it will be a better alternative for our sophisticated life style. The project is the very important and useful.

## 7. REFERENCE

[1]The PIC Microcontroller- Architecture, Programming and Applications Fangzhou, D., Zhenglong, L., Shaoqiang, Y., Beizhen, X. & Hong, L. (2011) Electricity generation directly using human feces wastewater for life support system. Acta Astronaut. 68 (9-10), 1537-1547.

[2]Futamata, H., Bretschger, O., Cheung, A., Kan, J., Owen, R. & Nealson, K.H. (2012) Adaptation of soil microbes during establishment of microbial fuel cell consortium fed with lactate. J. Biosci. Bioeng. [Online] xx (xx), 1-6. Available from: doi:10.1016/j.jbiosc.2012.07.016 [Accessed: 13 September 2012].

[3]Electronic Circuits and Devices [Boylestead] Ieropoulos, I., Greenman, J. & Melhuish, C. (2012) Urine utilisation by microbial fuel cells; energy fuel for the future. Phys. Chem. Chem. Phys.14 (1), 94-98.

[4]Ieropoulos, I. (2006) EcoBot: Towards an Energetically Autonomous Robot. PhD Thesis. University of the West of England, Bristol, UK.

[5]Ieropoulos, I., Greenman, J. & Melhuish, C. (2010b) EcoBot-III: a robot with guts. In: Proceedings of the Alfie XII conference. 2010 Denmark., pp. 733-740.

[6]Ieropoulos, I., Greenman, J. & Melhuish, C. (2008) Microbial fuel cells based on carbon veil electrodes: Stack configuration and scalability. Int. J. Energ. Res. 32, 1228-1240.

Dr.M G Gireeshan<sup>1</sup> **Research Scientist Biomedical department**, Bharath University, Chennai India MSc,MTech,MPhil PHD (Honorary USA) Email: mggireeshan@gmail.com

Akhilesh k<sup>2</sup> B.Tech (EEE) in Nehru College of Engineering and Research centre, Thrissur, Kerala.India.